ZuhauseBlogDetaillierte Anleitung zum vollständigen Addier

Detaillierte Anleitung zum vollständigen Addier

Im Bereich der digitalen Elektronik und Computertechnik repräsentieren Addierer einen der wichtigsten Bausteine, die bei der Konstruktion und Funktionalität komplizierterer arithmetischer Schaltungen entscheidend sind.Als integrale Komponenten der arithmetischen Logikeinheit (ALU) erleichtern Addler zahlreiche Computervorgänge, die von grundlegenden Arithmetik bis hin zu komplexen logischen Aufgaben reichen, die für Systemvorgänge erforderlich sind.Ihr Design, das von einfachen Halbadders bis hin zu komplexeren vollständigen Addierern variieren kann, spielt eine entscheidende Rolle bei der Verbesserung der Effizienz und Geschwindigkeit der Verarbeitung in digitalen Systemen.Dieser Artikel befasst sich mit der detaillierten Architektur und funktionalen Nuancen verschiedener Arten von Addierern und veranschaulicht ihre kritische Rolle in der modernen Computertechnologie und die Erforschung ihrer Betriebslogik, Schaltung und Anwendungen im breiteren Kontext des digitalen Logikdesigns.

Katalog

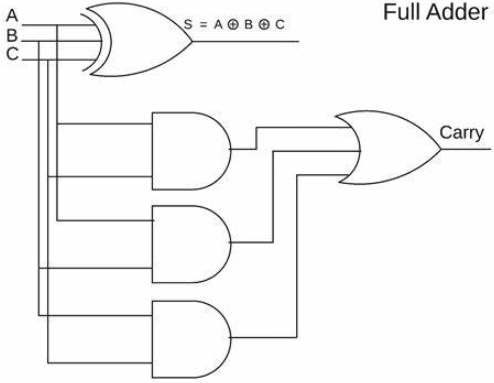

Abbildung 1: Voller Addierer

Ein Addierer ist eine grundlegende Komponente im Bereich Elektrotechnik und digitales Logikdesign und spielt eine zentrale Rolle in komplexeren Computersystemen.Als Teil der arithmetischen Logikeinheit (ALU) übernimmt der Addierer eine Vielzahl wesentlicher Computeraufgaben.Die Effizienz und Leistung des gesamten Prozessors wird direkt von der Gestaltung und Funktionalität des Addierers beeinflusst.

Im Prozessor wird der Addierer nicht nur für grundlegende arithmetische Operationen wie Addition und Subtraktion verwendet, sondern auch für eine breitere Palette von logischen Operationen.Zum Beispiel muss der Prozessor beim Ausführen von Programmen häufig neue Speicheradressen berechnen.Dies erfolgt in der Regel durch Hinzufügen oder Subtrahieren von der aktuellen Adresse - eine vom Addierer durchgeführte Aufgabe.Sie steuern die Anzahl der Schleifen -Iterationen und den Gesamtfluss durch Inkrementierung und Verringerung der Zähler.In komplexeren Anwendungen, wie z. B. der Tabellenindexierung, finden Addierer Daten schnell, indem sie Offsets berechnen.Dies ist wichtig für Datenbankverwaltungssysteme, Compiler-Konstruktion und groß angelegte Datenverarbeitung.Addierer sind auch der Schlüssel für die Implementierung bestimmter Mapping-Techniken in Multi-Level-Cache-Systemen, wobei arithmetische Operationen zur Bestimmung der Datenposition im Cache bestimmen und so den Zugriffseffizienz optimiert werden.

Technologisch werden Addierer über verschiedene Schaltungskonstruktionen implementiert, einschließlich paralleler, serieller und Pipeline -Addierer.Parallele Addierer sind für ihre Fähigkeit bevorzugt, mehrere Ziffern gleichzeitig zu verarbeiten, sodass sie für Szenarien geeignet sind, die eine schnelle Berechnung erfordern.Serielle Addierer verarbeiten dagegen einen Bit pro Taktzyklus und eignen sich ideal für ressourcenbegrenzte oder geringe Leistungsumgebungen.Pipeline -Addler teilen den Additionsprozess in mehrere Phasen, wobei jeder einen Teil des Additionsbetriebs bearbeitet.Dieses Design steigert die Rechengeschwindigkeit erheblich, insbesondere in Hochleistungs-Computerumgebungen.

Eine Halbadder-Schaltung ist ein grundlegender Baustein in der digitalen Elektronik, das speziell für zwei einzelne binäre Ziffern ausgelegt ist.Dieser Schaltkreis bildet die Grundlage eines vollständigen Addierers und ist der Schlüssel zum Verständnis komplexerer Logikschaltungsdesigns.In einem halben Addierer gibt es zwei primäre Eingänge mit der Bezeichnung A und B, die den Augend bzw. die Addend darstellen.Mit diesem Setup kann es die Summe berechnen und die Ausgabe tragen, ohne dass eine Trageingabe aus früheren Berechnungen erforderlich ist.

Der Kern einer Halbadder besteht aus zwei logischen Toren: einem XOR-Tor und einem und Tor.Das XOR -Gate ist für die Erzeugung der Summenausgabe verantwortlich.Es arbeitet unter einer einfachen Regel, in der es eine 1 ausgibt, wenn nur einer seiner Eingänge 1 ist;Andernfalls gibt es ein 0. Das und Gate gibt dagegen die Trageausgabe ab.Es erzeugt nur dann eine 1, wenn beide Eingaben 1 sind und perfekt mit den grundlegenden Anforderungen der binären Addition übereinstimmen.

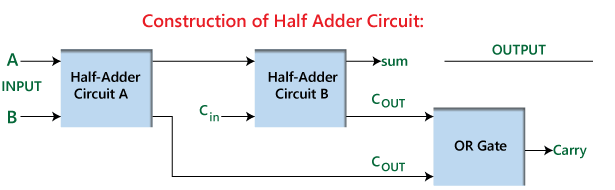

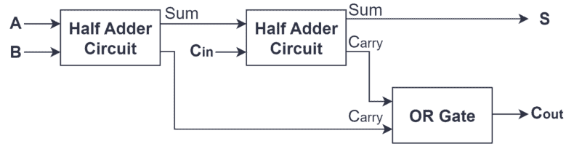

Abbildung 2: Konstruktion von Halbaddierern

Dieses effiziente und unkomplizierte Design ermöglicht es dem Halbaddier, nicht nur eine grundlegende binäre Ergänzung unabhängig voneinander durchzuführen, sondern auch als Baustein für die Erstellung eines vollständigen Addierers dienen.Ein vollständiger Addierer wird durch Kombination von zwei Halbzädern mit einem zusätzlichen oder Gate errichtet.In diesem Setup übernimmt der erste Hälfte die erste Additionsaufgabe, wodurch eine vorläufige Summe erzeugt und transportiert wird.Der Addierer der zweiten Halbzeit verarbeitet dann den Trage von Anfang an zusammen mit einem zusätzlichen Trageingang.Schließlich verschmelzen das oder Gate die beiden Trageausgänge, um die endgültige Trageausgabe zu erzeugen.Diese Anordnung verbessert die Funktionalität des Addierers und ermöglicht es ihm, komplexere Multi-Bit-Additionsaufgaben zu erledigen und die weit verbreitete Anwendung und die Bedeutung von Halbadern im Digital Circuit-Design zu präsentieren.

Ein Volladdierer ist eine fortschrittliche Komponente im digitalen Logikdesign, die für die Hinzufügung von drei Single-Bit-Binäreingängen ausgestattet ist, die häufig als A, B und Carry-In (CIN) gekennzeichnet sind.Dieses Design ermöglicht es dem vollständigen Addier, komplexe binäre Ergänzungen effizient zu verarbeiten, indem der Trage von früheren Berechnungen niedrigerer Ordnung in einen einzelnen Betrieb einbezogen wird.

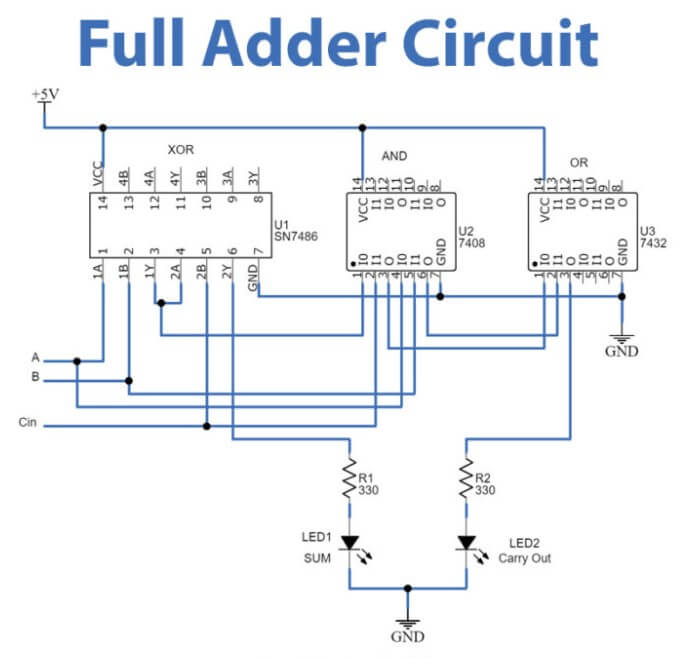

Abbildung 3: Voller Addiererschaltung

Funktionell kann ein vollständiger Addierer eine zweistellige Summe ausgeben, was bedeutet, dass sein Ausgang zwischen 0 und 3 reichen kann und auch eine Carry-Out (COUT) erzeugen kann.Dies geschieht, weil, wenn alle Eingangsbits auf 1 (a = 1, b = 1, cin = 1) eingestellt sind, die Summenausgabe 1 (Repräsentation binärer 01) und eine Durchführung von 1 erzeugt wird, was darauf hinweistEin zusätzlicher Trage muss zum nächsten höheren Bit übergeben werden.

Strukturell besteht der volle Addierer im Allgemeinen aus zwei Halbzädern und einem oder Tor.Der Addierer in der ersten Halbzeit nimmt die Eingänge A und B ein und erzeugt eine anfängliche Summe und ein Tragsignal.Diese anfängliche Summe wird dann zusammen mit dem Eintrag (CIN) in die zweite Halbadder gefüttert.Die Aufgabe des Addierers in der zweiten Halbzeit besteht darin, diese Summe von der ersten Hälfte zu CIN hinzuzufügen, wodurch eine weitere Summe und eine neue Tragausgabe erzeugt werden.Gleichzeitig werden die Trageausgabe aus der ersten Hälfte und die Trageausgabe aus der zweiten Hälfte durch ein oder ein Tor verschmolzen, der im endgültigen Carry-out (COUT) des vollen Addierers gipfelt.Das Design dieser Struktur stellt sicher, dass der vollständige Addierer die Ausbreitung von Trägern zusätzlich über Operationen ausgeht, wodurch es ideal für die Ausführung von Binärzusagen von mehreren Bit ist.Das Design des vollständigen Addierers beschleunigt nicht nur die Datenverarbeitung und verbessert die Effizienz, sondern vereinfacht auch die Komplexität der Hardware-Implementierung durch eine einfache Kombination von Logik-Gates und macht es zu einer unverzichtbaren Komponente in der multi-Digit-Addition und der arithmetischen Logikeinheit (Alu).

|

Parameter

|

Halbaddierer

|

Voller Addierer

|

|

Beschreibung

|

Halbaddierer ist eine Kombinationslogik

Schaltung, die zwei 1-Bit-Ziffern hinzufügt.Die Halbadder produziert eine Summe der beiden

Eingänge.

|

Ein voller Addierer ist eine kombinationale Logik

Schaltkreis, der einen Additionsbetrieb auf drei Ein-Bit-Binärzahlen durchführt.

Der volle Addierer erzeugt eine Summe der drei Eingänge und den Wert.

|

|

Vorheriger Trage

|

Der vorherige Trage wird nicht verwendet.

|

Der vorherige Carry wird verwendet.

|

|

Eingänge

|

In Half Addierer gibt es zwei Eingangsbits (a,,

B).

|

In voller Addierer gibt es drei Eingangsbits

(A, b, cIn).

|

|

Ausgänge

|

Der erzeugte Ausgang besteht aus zwei Bitsummen

und vom Eingang von 2 Bits tragen.

|

Der erzeugte Ausgang besteht aus zwei Bitsummen

und vom Eingang von 3 Bits tragen.

|

|

Benutzt als

|

Eine halbe Ader-Schaltung kann nicht verwendet werden

genauso wie eine vollständige Schaltung.

|

Eine vollständige Addiererschaltung kann an Ort und Stelle verwendet werden

von einem halben Addierer.

|

|

Besonderheit

|

Es ist einfach und einfach zu implementieren

|

Das Design eines vollen Addierers ist nicht als als

Einfach wie ein halber Addierer.

|

|

Logischer Ausdruck

|

Der logische Ausdruck für den halben Addier ist:

S = a⊕b;C = a*b.

|

Der logische Ausdruck für den vollen Addier ist:

S = a⊕b⊕cin;Caus= (a*b)+(cIn*(a⊕b)).

|

|

Logik -Tore

|

Es besteht aus einem Ex-oder einem Tor und einem und

Tor.

|

Es besteht aus zwei Ex-oder zwei und Toren,

und eins oder ein Tor.

|

|

Anwendungen

|

Es wird in Taschenrechnern, Computern, verwendet,

Geräte für digitale Messungen usw.

|

Es wird in mehreren Bit -Ergänzungen verwendet,

Digitale Prozessoren usw.

|

|

anderer Name

|

Es gibt keinen alternativen Namen für die Hälfte

Addierer.

|

Ein voller Addierer ist auch als Ripple-Wagen bekannt

Addierer.

|

Diagramm

1: Unterschied zwischen dem halben Addierer und dem vollen Addierer

Die Wahrheitstabelle eines vollständigen Addierers ist der Schlüssel zum Verständnis seiner operativen Logik und detailliert die genaue Beziehung zwischen binären Eingangskombinationen und ihren entsprechenden Ausgängen.Diese Tabelle zeigt alle potenziellen Eingabeszenarien und deren Ergebnisse und macht sie zu einem wesentlichen Werkzeug für das Design und die Überprüfung digitaler Logikschaltungen.Der vollständige Addierer verarbeitet drei Eingänge: A, B und ein Übertragung (CIN), von denen jeder entweder 0 oder 1 betragen kann. Dies führt zu acht möglichen Kombinationen von Eingängen.

Für jede dieser Kombinationen umfassen die Ausgänge aus dem vollen Addierer eine Summe (Summe) und eine Carry-Out (Cout).Die Summe ist die Modulo-2-Addition (XOR-Operation) der drei Eingänge-A, B und CIN.Die Durchführung tritt auf, wenn mindestens zwei der Eingangsbits 1 sind. Dies spiegelt die Fähigkeit des vollständigen Addierers wider, die Übertragung in sequentiellen Additionsvorgängen zu verarbeiten, um die Genauigkeit bei höheren Bitberechnungen zu gewährleisten.

Betrachten Sie zur Veranschaulichung das Eingangsszenario, in dem alle Eingänge 0 sind (a = 0, b = 0, c-in = 0).Die Ausgangssumme beträgt 0 und der Trage wird auch 0 sein, was darauf hinweist, dass es keine zusätzliche Summe oder Trage zum Verwalten gibt.Wenn nur ein Eingangsbit 1 beträgt, z. B. a = 1, b = 0, c-in = 0, beträgt die Ausgangssumme 1 ohne Trage, was zeigt, dass keine Übertragung auf ein höheres Bit übertragen werden muss.Wenn zwei Eingangsbits 1 sind, wie a = 1, b = 1, c-in = 0, beträgt die Ausgangssumme 0 (da 1+1 in Binärer und Modulo-2 in 0 entspricht), aber die Trage-OUT IS 1, was auf einen Trage hinweist, der zum nächsten höheren Bit übergeben werden muss.Das komplexeste Szenario tritt auf, wenn alle drei Eingangsbits 1 sind (a = 1, b = 1, c-in = 1);Die Ausgangssumme beträgt 1, und es gibt eine Durchführung von 1, was darauf hindeutet, dass das Carry Management auch in noch höheren Bits erforderlich sein kann.

|

A

|

B

|

CIn

|

S

|

Caus

|

|

0

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

1

|

0

|

|

0

|

1

|

0

|

1

|

0

|

|

0

|

1

|

1

|

0

|

1

|

|

1

|

0

|

0

|

1

|

0

|

|

1

|

0

|

1

|

0

|

1

|

|

1

|

1

|

0

|

0

|

1

|

|

1

|

1

|

1

|

1

|

1

|

Diagramm 2: Full Adder Wahrheitstabelle

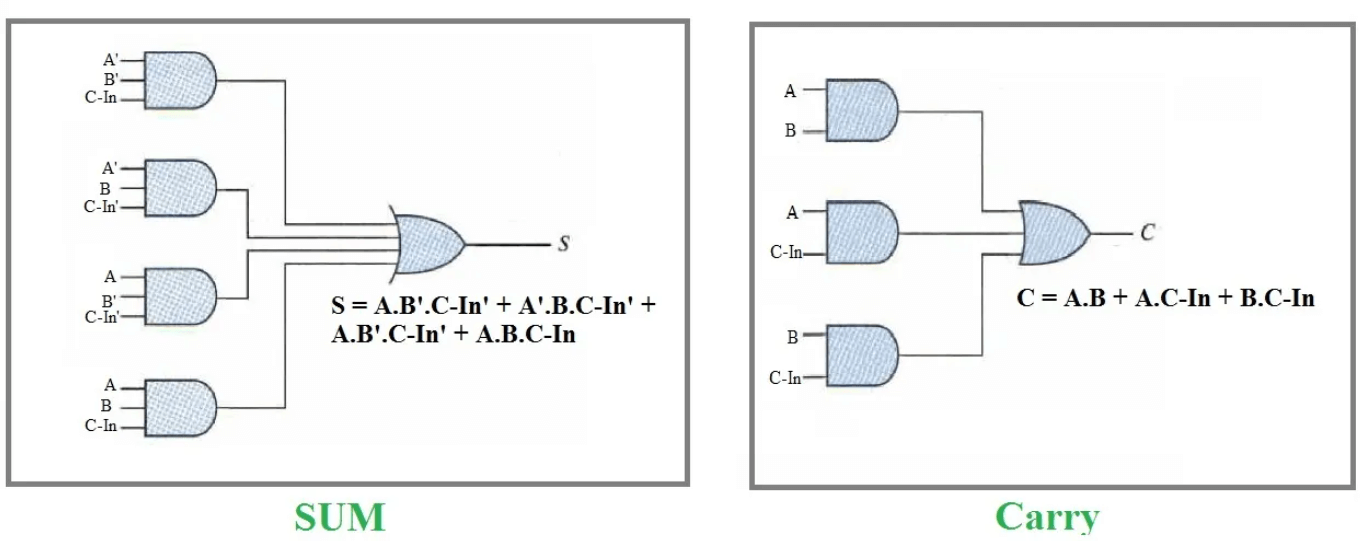

Das Verständnis des vollständigen Addierers beinhaltet die Analyse seiner Funktionalität mithilfe der Wahrheitstabelle, in der verschiedene Kombinationen von Eingangswerten A, B und C-In zu Ausgängen Summe und Cout führen.Um den Vorgang zu erfassen, vereinfachen wir die Logikgleichungen Schritt für Schritt.

Logischer Ausdruck für die Summe

Die Gleichung beginnt mit den unterschiedlichen Fällen, in denen die Summe entspricht 1:

• A 'B' CIN + A 'B CIN' + A B 'CIN' + AB CIN

Diese Gleichung kann durch Gruppierung von Begriffen mit und ohne CIN verdichtet werden:

• CIN (A 'B' + AB) + CIN '(A' B + A B ')

Diese Vereinfachung führt zu einer leichteren Implementform:

• cin xor (a xor b)

Diese Darstellung zeigt, dass die Summenausgabe im Wesentlichen der XOR -Betrieb zwischen A, B und CIN ist und das Kernverhalten der binären Addition erfasst, bei dem die Summe basierend auf einer ungeraden Anzahl von Einsen umschaltet.

Logik für Cout

Beginnend mit Bedingungen, unter denen der Trage erzeugt wird:

• A 'B cin + a b' Cin + ab C-In ' + ab CIN

Wenn wir die Gleichung vereinfachen, identifizieren wir Begriffe, die üblicherweise eine Trage erzeugen:

• AB + B cin + a cin

Auf der Suche nach einer anderen Methode zur Implementierung von Cout kann die Gleichung neu organisiert werden:

• AB + A CIN + B C-In (a + a ')

Dies erweitert sich und rekombiniert, um alle Szenarien zu erfassen, in denen mindestens zwei Eingaben 1 sind:

• AB CIN + AB + A C-IN + A 'B CIN

• AB (1 + cin) + a c-in + a 'b cin

• AB + A C-In (B + B ') + A' B cin

• AB + A B 'CIN + A' B CIN

• AB + CIN (A 'B + A B')

Die endgültige kompakte Form für Cout:

• AB + cin (a xor b)

Diese Version der Carry-Out-Gleichung zeigt, wie Cout entweder wenn sowohl A als auch B 1 oder wenn einer von A oder B zusammen mit einem Übertragungen erzeugt wird, und somit die Logik verkörpertBit Binärer Zusatz.Diese optimierte Logik ist besonders nützlich, um effiziente digitale Schaltkreise zu implementieren.

Abbildung 4: Gleichungen eines vollständigen Addierers

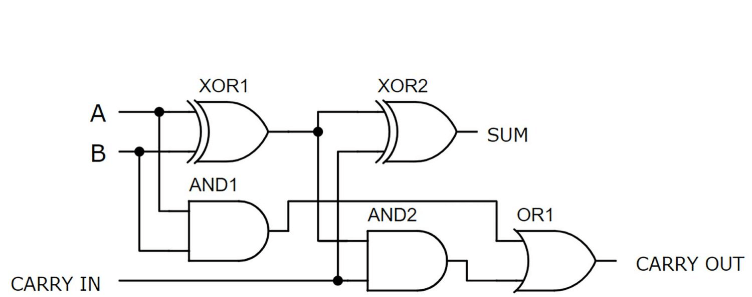

Durch die Implementierung einer vollständigen Addiererschaltung werden zwei Halbadler und ein oder ein Gate sorgfältig zusammengestellt, um ein Gerät zu erstellen, das die Zugabe von drei Einzelbit-Binäreingängen effizient behandeln kann.Diese Anordnung optimiert die Komplexität des Schaltkreises und sorgt sowohl für effiziente als auch genaue Berechnungen.

Zu Beginn nimmt der erste Hälfte zwei primäre Binäreingänge, A und B, die Hauptniffern, die hinzugefügt werden.Seine Schlüsselaufgabe ist die Berechnung der Summe und der anfänglichen Trage dieser beiden Zahlen.Hier liefert der erste Hälfte Addierer zwei Ergebnisse: eine anfängliche Summe (SUM1) und einen ersten Carry (Carry1).SUM1 wird aus dem XOR -Betrieb von A und B abgeleitet, was angibt, ob die Gesamtsumme eine ungerade Anzahl von 1 hat.Carry1, das Ergebnis des und Betriebs zwischen A und B, zeigt an, ob beide Ziffern 1 sind, was einen Übertrag zum nächsten höheren Bit erfordert.

Als nächstes schließt sich der Addierer der zweiten Hälfte dem Prozess an.Es verwendet die Summenausgabe SUM1 und das dritte Eingangscin (Übertragung einer früheren Berechnung) als Eingänge.Der Addierer der zweiten Halbzeit erzeugt zwei Ausgänge: das endgültige Summeergebnis (SUM2) und das sekundäre Carry (Carry2).SUM2, das das XOR -Ergebnis von SUM1 und CIN ist, repräsentiert die endgültige Summe der drei Eingänge und zeigt die aggregierte binäre Addition an.Carry2, der aus dem und Betrieb zwischen SUM1 und CIN entsteht, zeigt einen von diesen Komponenten erzeugten Trage an.

Abbildung 5: Voller Addiererkreis mit zwei Halbaddierern

Um das Design des vollständigen Addierers zu vervollständigen, muss ein oder ein Gate die Tragausgänge von Carry1 und Carry2 von beiden Halbadern verarbeiten.Dieses oder ein Tor stellt sicher, dass jeder Trage, der während der Berechnungen erzeugt wird, korrekt an die endgültige Ausgabe weitergeleitet wird.Daher ist der endgültige Carry Output (COUT) des vollständigen Addierers das oder Ergebnis von Carry1 und Carry2.Die Einbeziehung dieser oder des Gate garantiert, dass alle potenziellen Trages genau berechnet und in mehreren Bit-Additionsvorgängen auf die nächste Ebene übertragen werden, um die Integrität des arithmetischen Betriebs über mehrere Bits hinweg zu gewährleisten.

Vollständige Addierer spielen eine unverzichtbare Rolle im digitalen Logikdesign und bieten zahlreiche Vorteile, die sie in verschiedenen Computer- und Datenverarbeitungsszenarien wesentlich machen.Ihre Hauptvorteile zählen bemerkenswerte Flexibilität, schnelle Verarbeitungsgeschwindigkeiten und ein effizientes Tragemanagement.Diese Merkmale machen vollständige Addlers ideal, um komplexe arithmetische Operationen und Logikfunktionen auszuführen, insbesondere bei Anwendungen, die eine sequentielle Multi-Bit-Addition erfordern.

Vorteile

Flexibilität: Vollständige Addierer übertreffen ihre Fähigkeit, mehrere binäre Eingaben gleichzeitig (A, B und CIN) zu verarbeiten.Sie können auch in größere Adder -Arrays erweitert werden, um längere Binärzahlen zu verarbeiten.Diese Skalierbarkeit ist wichtig, um Hochleistungs-Arithmetik-Logikeinheiten (ALUs) aufzubauen, die komplizierte Multi-Bit-Arithmetik- und Logikoperationen ausführen müssen.

Geschwindigkeit: Dank ihrer internen parallelen Verarbeitungsarchitektur können vollständige Addierer die Hinzufügung aller Eingänge in einem einzelnen Taktzyklus vervollständigen und gleichzeitig feststellen, Ausgänge zu tragen.Diese Fähigkeit unterstützt kontinuierliche Additionsvorgänge und ist für die Echtzeitdatenverarbeitung in modernen Mikroprozessoren und Hochgeschwindigkeits-Computergeräten unverzichtbar.

Nachteile

Vollständige Addierer stellen jedoch auch bemerkenswerte Nachteile vor:

Komplexität bei Design und Implementierung: Vollständige Addierer umfassen mehrere Logik-Gates und mehrstufige Tragverbreitung, wodurch deren Design komplex gestaltet wird.Diese Komplexität erhöht nicht nur die Herstellungskosten, sondern kann auch die Zuverlässigkeit der Schaltkreise beeinflussen.

Ausbreitungsverzögerungsprobleme: Die Trageverbreitung kann mehrere Logiktore durchlaufen, wobei jeweils ihre Verzögerung hinzugefügt wird.Dies kann die gesamte Rechengeschwindigkeit während groß angelegter Vorgänge einschränken, insbesondere in umfangreichen Computersystemen und bei der Gestaltung der Integration (VLSI) und Hochgeschwindigkeitsprozessoren im Bereich der sehr großen Maßstab.Die Verzögerung kann zu einem erheblichen Engpass in der Leistung werden.

Um diese Probleme zu mildern, untersuchen die Ingenieure kontinuierlich effizientere Schaltungskonstruktionen.Zu den Strategien gehören die Verwendung schnellerer Logik-Gate-Technologien, Optimierung von Schaltungslayouts, um die Pfadlängen zu verkürzen, und die Entwicklung fortschrittlicher Technologien wie Carry-Save-Addierer, um Verzögerungen bei der Ausbreitung von Trage zu minimieren.

Vollständige Addierer werden ausgiebig in der digitalen Logik eingesetzt, die für ihre Flexibilität und Effizienz geschätzt werden, wodurch sie für eine Vielzahl von Computer- und Datenverarbeitungsaufgaben von zentraler Bedeutung sind.Ihre Anwendung erstreckt sich über grundlegende arithmetische Operationen über komplexe Signalverarbeitung und Systemsteuerung.Hier finden Sie einen detaillierten Blick auf einige wichtige Bereiche, in denen vollständige Addierer integriert sind.

Arithmetische Schaltungen

Einer der einfachsten Verwendungen von vollständigen Addierern ist in arithmetischen Schaltungen, in denen sie eine binäre Ergänzung durchführen.Besonders entscheidend für die Mehrbitennummer-Addition werden vollständige Addierer durch Kaskadierung längere binäre Sequenzen verwalten.In dieser Arrangement übernimmt jeder vollständige Addierer die Zugabe für seine Bitposition und den Trag vom unteren Bit und übergeht dann den neuen Carry zum vollen Addierer des nächsten höheren Bits.Diese Kaskade ermöglicht eine umfassende Multi-Bit-Ergänzung über den gesamten Bereich der Ziffern.

Datenverarbeitung

Vollständige Addler spielen auch eine entscheidende Rolle bei erweiterten Datenverarbeitungsaufgaben wie digitaler Signalverarbeitung (DSP) für Filterung und Fourier -Transformationen, bei denen präzise und schnelle arithmetische Operationen erforderlich sind.Darüber hinaus sind im Bereich der Informationssicherheit, einschließlich Datenverschlüsselung und Fehlererkennung und Korrekturalgorithmen wie Paritätsprüfungen und CRC -Codeerzeugung (Cyclic Redundancy Check), für die Ausführung wesentlicher Bitvorgänge von entscheidender Bedeutung.

Zähler

In digitalen Zählern sind vollständige Addierer für die Implementierung von Inkrement- und Dekrementfunktionen, insbesondere in modularen und synchronen Zählern, unverzichtbar.Sie verwalten Carry und leihen sich genau, um eine präzise Zählung sicherzustellen.

Multiplexer (MUX) und Demultiplexer (Demux)

In Multiplexern und Demultiplexern spielen vollständige Addierer eine entscheidende Rolle bei der Kanalauswahl und der Datenverteilung.Sie nehmen an der Logik teil, die feststellt, welche Kanäle für die Dateneingabe und -ausgabe verwendet werden, wodurch Entscheidungen auf der Grundlage von Logiksteuerungssignalen getroffen werden.

Speichertechnologie

In der Speicheradressierung helfen vollständige Addierer dabei, Adresssignale für den dynamischen Zugriff auf Speicherorte zu generieren.Dies ist besonders wichtig für den dynamischen Zufallszugriffsspeicher (DRAM) und andere Speichersysteme, bei denen vollständige Addierer komplexe Adressberechnungen unterstützen, um die Effizienz des Speicherzugriffs zu verbessern.

Arithmetische Logikeinheiten (Alu)

Als grundlegende Komponenten von arithmetischen Logikeinheiten in Mikroprozessoren und digitalen Signalprozessoren sind schließlich vollständige Addierer von entscheidender Bedeutung.Die ALU erledigt alle arithmetischen und logischen Operationen, wobei vollständige Addierer sicherstellen, dass Daten sowohl schnell als auch genau verarbeitet werden.

Vollständige Addierer können mit verschiedenen Logik -Toren und -konfigurationen konstruiert werden.Hier untersuchen wir vier verschiedene Implementierungen und zeigen ihre Setup- und operativen Nuancen hervor.

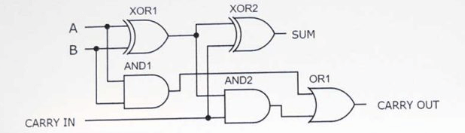

Voller Addierer mit Xor und und oder Toren gebaut

Abbildung 6: Voller Addierer, der mit XOR und und oder Logiktoren erstellt wurde

Dieses Beispiel zeigt einen vollständigen Addierer, der mit diskreten Transistoren auf einem Brotbrett gebaut ist.Die Konfiguration umfasst fünf logische Tore: zwei XOR -Gates, zwei und Gates und ein oder ein Gate, die insgesamt 21 Transistoren erfordern.Die Eingänge A und B sind mit der oberen linken Breadboard angeschlossen und erhalten eine +5 -V -Versorgung.Diese Eingänge werden mit zwei Kippschalter gesteuert.Zwei LEDs oben links geben die Zustände der Eingänge A und B an, während zwei LEDs auf der rechten Seite die Ausgänge anzeigen.Die in der Schaltung verwendeten Widerstände sind alle 2,2 km Ohm.Wenn die Eingänge A und B eingeschaltet sind und das Übertrag ausgeschaltet ist, zeigt der Ausgang einen Binärwert von 10, der die Summe 2 (1 + 1 + 0 = 10) darstellt.Die mit den ersten 12 Transistoren gebauten XOR-Gates verarbeiten die primäre Summierung, während die untere Hälfte des Brotbretts die und und und oder die Tore für Tragvorgänge enthält, farbcodierte Verkabelung verstärkt die Klarheit und Fehlerbehebung.

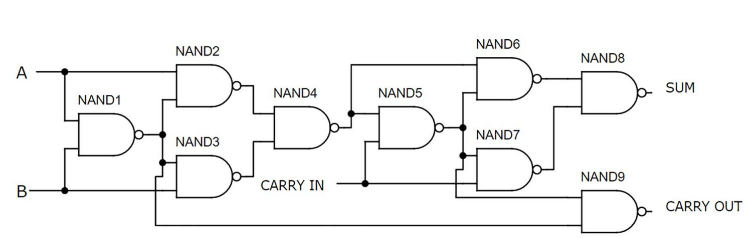

Voller Addierer mit Nand -Toren

Abbildung 7: Voller Addierer mit NAND -Toren

Dieser volle Addierer verwendet neun NAND -Tore, wobei jedes Tor aus zwei Transistoren mit insgesamt 18 Transistoren hergestellt wird.Diese Methode gehört zu den einfachsten und effizientesten Methoden, um einen vollständigen Adder mit diskreten Komponenten zu konstruieren.Alle Tore sind in der oberen Hälfte des Brotbretts zusammengestellt, während Schalter die untere Hälfte einnehmen.Die Funktionalität des Schaltkreises wird mit Eingängen A und B und dem Abnahme des Abschlusses demonstriert, was zu einem Ausgangs-Binärwert von 10 führt, der dem Dezimalzahl 2 entspricht.

Voller Addierer mit Nor Toren

Abbildung 8: Voller Addierer mit Nor Toren

Mit neun noch Toren, die jeweils zwei Transistoren benötigen, verwendet dieses Setup auch insgesamt 18 Transistoren.Der Aufbau eines vollständigen Addiers mit Nor Gates bietet eine gute Alternative, beinhaltet jedoch eine komplexere Verkabelung im Vergleich zu NAND -Toren.Jeder Transistor in den Nor Toren ist geerdet, wobei die Sammler von orangefarbenen Jumper -Kabeln verbunden sind, um eine ordentliche und organisierte Verkabelung zu gewährleisten.Diese Konfiguration wird mit den Eingängen A und B aktiviert und dem Eintrag deaktiviert, was zu den Ausgängen führt, in denen der Trage aktiv ist und die Summe ausgeschaltet ist.

Während dieser Erkundung der Adder -Technologie, von grundlegenden Halbaddern bis hin zu hoch entwickelten Adder -Designs, ist es offensichtlich, dass diese Komponenten grundlegend für die Weiterentwicklung digitaler Elektronik sind.Die operativen Merkmale und Implementierungsbeispiele lieferten die Vielseitigkeit und Effizienz von Addierern in verschiedenen Recheneinstellungen.Durch die Untersuchung der Struktur und Funktion von Addern, insbesondere durch ihre Wahrheitstabellen und charakteristischen Gleichungen, erhalten wir wertvolle Einblicke in ihre Fähigkeiten und Einschränkungen.Dieses Wissen ist maßgeblich an der Förderung des Designs effizientere und schnellere Computersysteme beteiligt.Letztendlich vereinfachen Addierer nicht nur komplexe Binärberechnungen, sondern ermöglichen auch die Verbreitung von Technologie in so unterschiedlichen Bereichen wie Datenverarbeitung, Speicherzuweisung und digitaler Signalverarbeitung.Während sich die digitale Technologie entwickelt, wird die anhaltende Verfeinerung und Innovation im Adder -Design weiterhin ein Eckpfeiler für die Entwicklung fortschrittlicherer Rechenarchitekturen sein, um sicherzustellen, dass diese grundlegenden Komponenten im Mittelpunkt des Designs und der Implementierung des digitalen Systems stehen.

Häufig gestellte Fragen [FAQ]

1. Was ist eine vollständige Addiererschaltung?

Ein Volladdierer ist eine digitale Schaltung, die drei binäre Bits hinzufügt, um eine Summe und einen Tragausgang zu erzeugen.Es ist für die Zugabe von drei Eingängen ausgelegt: zwei signifikante Bits und ein Eintragsbit aus einer früheren Addition.Auf diese Weise kann es in aufeinanderfolgenden Phasen verwendet werden, um mehr Bit-Binärzahlen hinzuzufügen.

2. Wie viele und, oder xor im vollen Addierer?

Ein typischer Volladdierer enthält:

Zwei Xor -Gates zum Erzeugen der Summe.

Zwei und Tore, um zur Berechnung der Carry beizutragen.

Eins oder ein Tor, um die Ausgangsleistung abzuschließen.

3. Was ist Carry Input in Full Addierer?

Der Carry Input (CIN) in einem vollständigen Addierer ist das Tragenbit aus der Zugabe der vorherigen, signifikanten Bits in mehreren Bit-Binärzusatz.Es ermöglicht dem vollständigen Addierer diesen vorherigen Carry bei der Berechnung der aktuellen Summe und des neuen Carry-Outs.

4. Warum einen vollen Addierer anstelle eines halben Addierers verwenden?

Ein Volladdierer wird anstelle eines halben Addierers verwendet, da er drei Bits (einschließlich des Tragens von früheren Ergänzungen) hinzufügen kann, wodurch er zum Zusammenketten geeignet ist, um Multi-Bit-Zahlen hinzuzufügen.Eine Halbadder kann nur zwei Bits hinzufügen und keine Bestimmung für eine Übertragung vorliegt, die ihre Verwendung auf die einfachsten Formen der binären Addition ohne sequentielle Trageverbreitung einschränkt.