Innovativer Leitfaden für JK Flip-Flops: Analyse von Wahrheitstabellen, Mechanismen und strategischen Anwendungen

In diesem Artikel wird die Architektur, den Betrieb und die verschiedenen Anwendungen des JK Flip-Flop unter der Ausnahme von grundlegenden Struktur und Eingabe-Output-Beziehungen über detaillierte Betriebsmechanik zu seinen strategischen Implementierungen in komplexen digitalen Systemen untersucht.Der Diskurs erstreckt sich auf die Unterscheidung zwischen den von Kanten ausgelösten und stehenden Varianten und analysiert ihre jeweiligen Versorgungsunternehmen in synchronen und asynchronen Umgebungen.Katalog

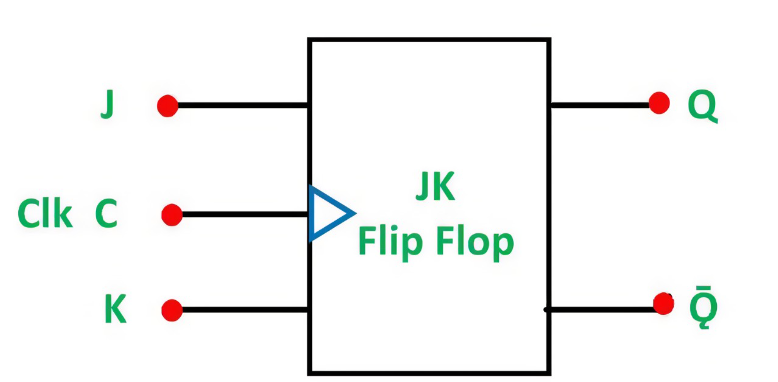

Abbildung 1: JK Flip-Flop

Grundlagen von JK Flip-Flop

Der JK Flip-Flop ist eine grundlegende Komponente in der digitalen Elektronik, mit der ein einziges Stück Informationen gespeichert werden können.Es baut auf dem einfacheren SR-Flip-Flop auf, indem Feedback hinzugefügt wird, wodurch Fehler verhindert werden, die als "Rassenbedingungen" bezeichnet werden, bei denen die Ausgabe instabil wird.

Dieser Flip-Flop verfügt über zwei Haupteingänge, J (SET) und K (Reset) sowie zwei Ausgänge: Q und seine Komplement, Q '.Diese Ausgänge spiegeln kontinuierlich den aktuellen Zustand und das Gegenteil wider, sodass die Schaltung die Echtzeit-Eingangsänderungen einstellen und reagieren kann.

Der JK Flip-Flop arbeitet auf bestimmte Weise basierend auf den Eingabewerten:

• Wenn sowohl J als auch K 0 sind: Der Flip-Flop hält seinen aktuellen Zustand.Es treten keine Änderungen auf.

• Wenn sowohl J als auch K 1 sind: Der Flip-Flop schaltet seinen Zustand um.Wenn Q 0 ist, wird es 1;Wenn Q 1 ist, wechselt es auf 0. Diese Umschaltungsaktion ist eine Schlüsselfunktion, die den JK-Flip-Flop von einfacheren Designs unterscheidet.

• Wenn J 1 und k ist 0: Der Flip-Flop stellt seinen Zustand fest und macht Q gleich 1.

• Wenn J 0 und k ist 1: Der Flip-Flop wird zurückgesetzt, wodurch Q gleich 0 ist.

Betrieb des JK Flip-Flops

Das JK Flip-Flop spielt eine Schlüsselrolle in digitalen Schaltkreisen, indem er Speicher und Timing durch eine koordinierte Reaktion auf Eingangssignale und Taktimpulse verwaltet.Sein Betrieb hängt stark vom Zeitpunkt der J- und K -Eingänge in Bezug auf das Taktsignal ab, das bestimmt, wie sich der Ausgangszustand (Q und Q̅) verändert.Diese Synchronisation stellt sicher, dass sich der Flip-Flop in verschiedenen Schaltungsanwendungen vorhersehbar verhält.Der Flip-Flop stützt sich auf NAND oder NOR Gates, um diese Zustandsänderungen zu verwalten.

Den aktuellen Zustand halten- Wenn sowohl J- als auch K-Eingänge niedrig sind (0), hält der Flip-Flop seinen aktuellen Zustand.Die Logik -Tore "sperren" die Ausgänge effektiv und stellen sicher, dass der vorherige Zustand (entweder hoch oder niedrig) beibehalten wird.Diese Haltefunktion ist in Anwendungen schwerwiegend, bei denen Daten stabil bleiben müssen, bis eine bestimmte Änderung ein Muss ist.

Einstellen des Ausgangs hoch (Set Status) -Wenn der Taktimpuls auftritt und J hoch (1) ist, während K niedrig bleibt (0), stellen sich die Logik-Tore ein, um den Flip-Flop einzustellen.Dies treibt die Ausgabe Q zu einem hohen Zustand (1) an.Dies ist nützlich in Situationen, in denen die Schaltung eine hohe Ausgabe auslösen muss, z. B. ein Gerät aktiviert oder ein "1" im Speicher speichert.

Löschen des Ausgangs niedrig (Status zurücksetzen) - Wenn J niedrig (0) und K zum Zeitpunkt eines Taktpulses hoch (1) ist, übergeht der Flip-Flop zu einem Reset-Zustand, wodurch Q gezwungen wird, niedrig zu werden (0).Diese Rücksetzaktion wird häufig in Schaltungen verwendet, die nach Abschluss eines Vorgangs einen Standard- oder Löschenstatus erfordern, z. B. die Löschung von Daten aus dem Speicher.

Die Ausgabe umschalten - Die einzigartige Funktion des Flip-Flop entsteht, wenn sowohl J als auch K hoch sind (1).Wenn der Taktimpuls eintrifft, schaltet der Flip-Flop um und schaltet den Ausgang von seinem Stromzustand auf das gegenüberliegende.Wenn Q hoch ist, wird es niedrig und wenn Q niedrig ist, wird es hoch.Diese Umschaltfunktion besteht in Anwendungen wie Zählern oder Geräten, die sich automatisch zwischen den Zuständen abwechseln müssen.

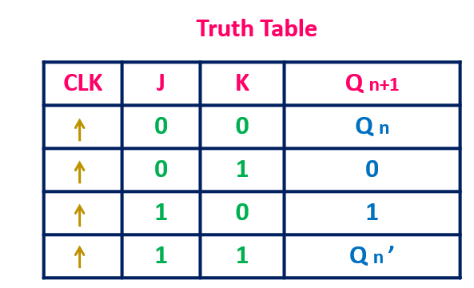

Abbildung 2: JK Flip-Flop Wahrheitstabelle

JK Flip-Flop Wahrheitstabelle Analyse

Die Wahrheitstabelle des JK Flip-Flop ist ein Schlüsselwerkzeug, um die Synchronisierung mit Taktimpulsen auf verschiedene Eingangssignale zu visagieren.Diese Tabelle hilft sowohl beim Entwerfen als auch bei der Fehlerbehebung digitale Schaltkreise, indem gezeigt wird, wie sich die Ausgänge des Flip-Flop basierend auf verschiedenen Eingangsbedingungen ändern.

• Sowohl J als auch K niedrig (J = 0, k = 0): Wenn beide Eingänge 0 sind, hält der Flip-Flop ihren aktuellen Zustand.Ob Q hoch oder niedrig ist, es bleibt unverändert.Dies ist für Schaltungen bemerkenswert, bei denen eine stabile Datenbindung gewünscht wird, wie z. B. In-Memory-Elemente, in denen die Erhaltung des aktuellen Zustands geeignet ist, bis eine bestimmte Änderung ausgelöst wird.

• j hoch, k niedrig (J = 1, k = 0): Wenn J 1 und k 0 ist, legt der Flip-Flop die Ausgangs q auf hoch (1).Diese Einstellungsbedingung ist nützlich für Anwendungen, die einen präzisen Auslöser benötigen, um einen Vorgang zu aktivieren, z. B. ein Gerät einschalten oder eine Sequenz in einem Logikkreis einleiten.

• J niedrig, k hoch (j = 0, k = 1): Mit J bei 0 und K bei 1 wird der Flip-Flop zurückgesetzt, wodurch Q niedrig ist (0).Diese Reset -Funktion ist in Systemen schwerwiegend, die in einen Standardzustand zurückkehren müssen, z. B. beim Löschen von Daten oder beim Initialisieren eines Prozesses.

• Sowohl J als auch K hoch (J = 1, k = 1): Wenn beide Eingänge hoch sind, schaltet der Flip-Flop seinen Zustand um.Wenn q hoch ist, wird es niedrig und wenn Q niedrig ist, schaltet es auf hoch.Dieses Umschaltverhalten ist für Geräte, die sich zwischen Zuständen wechseln, erheblich, z.

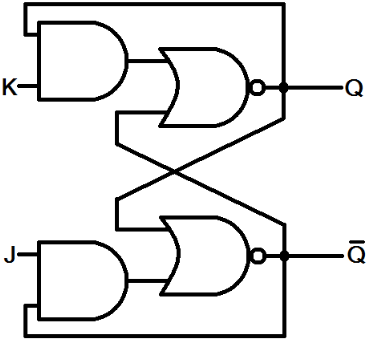

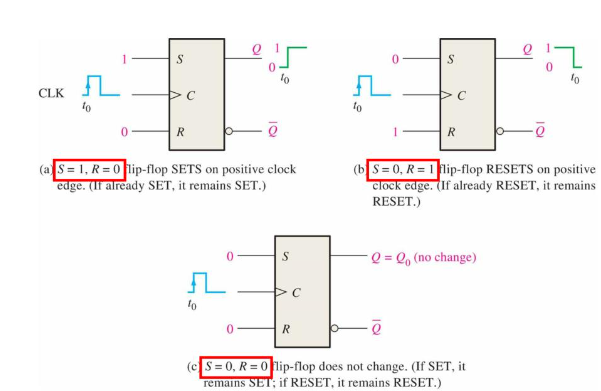

Abbildung 3: JK -Verriegelung

Erkenntnisse in den JK -Latch -Betrieb und verwendet

Der JK-Latch arbeitet ähnlich wie das JK Flip-Flop, ohne jedoch ein Taktsignal erforderlich.Anstatt auf eine Taktkante zu warten, reagiert der JK-Verriegelung kontinuierlich auf Eingabedändere, sodass sie "Level-sensitiv" macht.Dies bedeutet, dass sich die Ausgabe in Echtzeit ändert und so lange die Eingänge (j und k) stabil sind und sofortige Rückkopplungen basierend auf den Eingangsbedingungen bieten.

Im Gegensatz zum kandnollen ausgelösten JK Flip-Flop, der seine Ausgabe nur dann aktualisiert, wenn sich das Taktsignal ändert (von niedrig zu hoch oder umgekehrt), passt der JK-Latch seine Ausgabe sofort ein, wenn die Eingänge verschoben werden.Diese konstante Reaktionsfähigkeit in Echtzeit ist in Szenarien wertvoll, in denen sofortige Handlung ohne die durch Taktsynchronisation verursachte Verzögerung gewünscht wird.

Geräuschfilter: In digitalen Schaltkreisen, die schnell unerwünschtes Rauschen herausfiltern müssen, ist die sofortige Reaktion des JK -Latches auf Eingangsänderungen einflussreich.Da es nicht auf einen Taktpuls wartet, kann er den Ausgang einstellen, sobald das Geräusch erfasst wird, wodurch Verzögerungen bei der Signalkorrektur verhindern.

Einfache Speicherelemente: Der JK -Latch kann als grundlegende Speichereinheit in Systemen dienen, für die keine komplexe und taktete Steuerung erforderlich ist.Da der Latch den Ausgang stabil hält, solange sich die Eingänge nicht ändern, hält er den aktuellen Zustand effektiv, was für Schaltungen nützlich ist, die Informationen ohne den Overhead von Taktvorgängen aufbewahren müssen.

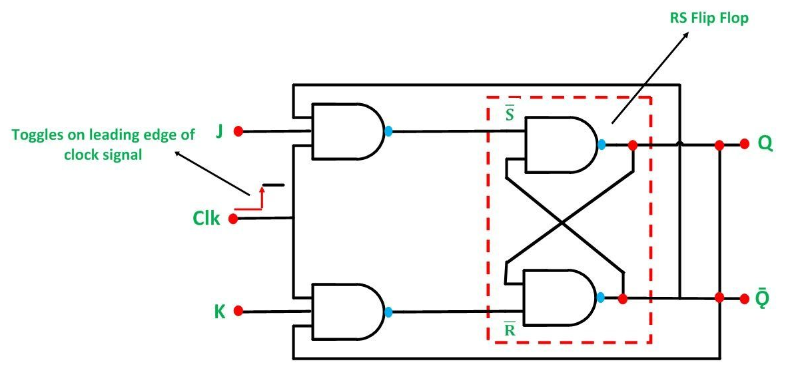

Abbildung 4: Timing-Diagrammanalyse für das JK Flip-Flop

Analyse des Timing-Diagramms von JK Flip-Flops

Ein Zeitdiagramm des JK Flip-Flop bietet eine visuelle Aufschlüsselung der Reaktion der Ausgabe auf verschiedene Eingänge, die mit den Impulsübergängen der Uhr synchronisiert sind.Dieses Diagramm zeigt die Beziehung zwischen dem Taktsignal (CLK) und den Eingängen (J und K) und der Art und Weise, wie sie die Ausgänge (Q und Q ') gemeinsam beeinflussen.Es hilft, das Verhalten des Flip-Flop über sequentielle Zustände hinweg abzubilden, was es einfacher macht, seine Operation zu verstehen.

Erstens das Diagramm Highlights, dass die Ausgänge nur an den steigenden oder fallenden Kanten des Taktpulses aktualisiert werden.Diese Funktion, die als Kantenauslöser bezeichnet wird, ist dominant für den Betrieb des JK Flip-Flop.Es zeigt, dass sich die Ausgabe, selbst wenn sich die Eingänge J und K ändern, unverändert bleibt, bis die Taktkante auftritt, was vorhersehbare und stabile Übergänge gewährleistet.

Dann, wenn das Diagramm die Variationen der Eingänge j und k abbildert, visuell zeigt, wie sich jede Eingangskombination auf die Ausgabe auswirkt. Wenn beispielsweise sowohl J als auch K niedrig sind (0), hält der Ausgang seinen aktuellen Zustand.Wenn J hoch ist und K niedrig ist, wird der Ausgang eingestellt.Diese klare visuelle Darstellung hilft den Benutzern zu verstehen, wie der Flip-Flop in Echtzeit auf verschiedene Eingabekombinationen reagiert.

Endlich, Das Timing -Diagramm zeigt deutlich die Übergänge zwischen verschiedenen Ausgangszuständen, egal ob das Halten, Einstellen, Zurücksetzen oder Umschalten.Jede Zustandsänderung ist direkt an die Eingabebedingungen und die Taktkante gebunden und zeigt eine Ursache-Wirkungs-Beziehung, die sich auf die Gestaltung und Fehlerbehebung konzentriert.

Vielseitige Anwendungen von JK Flip-Flops

JK Flip-Flops sind Kernkomponenten in einer Vielzahl von digitalen Systemen, die für ihre Flexibilität und Zuverlässigkeit bekannt sind.Ihre Fähigkeit, komplexe logische Operationen zu handhaben, macht sie in mehreren wichtigen Anwendungen erforderlich, darunter:

Abbildung 5: Speicherspeicher

JK Flip-Flops werden üblicherweise verwendet, um einzelne Datenbits zu speichern, wodurch sie grundlegende Elemente in Speicherarrays und Registern machen.Jedes Flip-Flop enthält ein Bit, um eine zuverlässige Datenspeicherung zu gewährleisten, was für die Gestaltung größerer Speichersysteme von Vorteil ist.

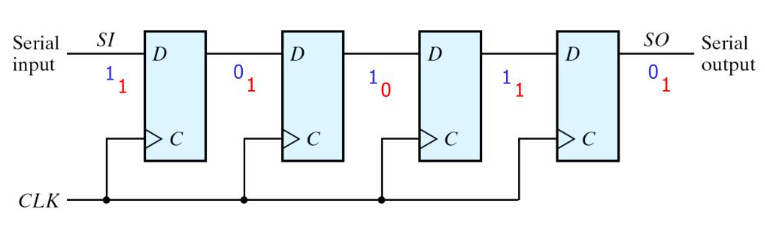

Abbildung 6: Zähler und Schichtregister

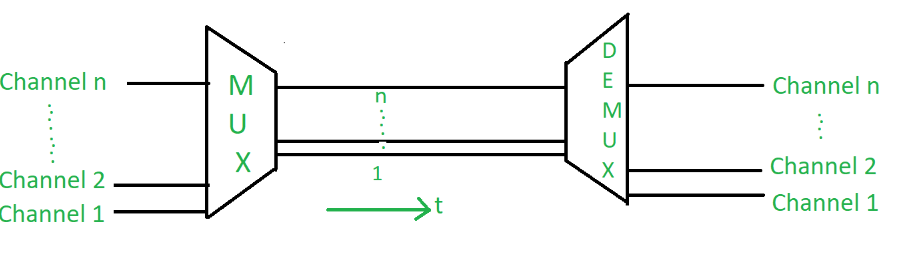

JK Flip-Flops sind bei Sequenzierungsoperationen dynamisch.Sie werden häufig in Zählern zum Zählen von Ereignissen oder Impulsen und in Schichtregistern zum Umwandeln von Seriendaten in parallele Formate verwendet.Dies macht sie nützlich, um Daten in verschiedenen Phasen eines Prozesses zu verwalten und zu manipulieren, z. B. in Kommunikationssystemen.

Abbildung 7: Frequenzteilung

Bei der Signalverarbeitung werden JK Flip-Flops häufig für die Frequenzteilung verwendet.Durch den Umschalten ihres Zustands mit jedem Taktpuls teilen sie die Frequenz des Eingangssignals und erzeugen ein langsameres, überschaubareres Taktsignal.Dies ist in Anwendungen wie der Taktsignalverwaltung bemerkenswert, bei denen die Zeitsteuerung gewünscht wird.

Abbildung 8: Synchronisation

JK Flip-Flops helfen dabei, mehrere digitale Prozesse zu synchronisieren, indem sichergestellt wird, dass verschiedene Teile eines Systems koordiniert zusammenarbeiten.Sie stellen sicher, dass verschiedene Komponenten korrekt auf zeitgesteuerte Signale reagieren und das gesamte System synchronisiert halten.

Abbildung 9: JK Flip-Flop: Kanten ausgelöst und ausgestrahlt

Verschiedene Arten von JK Flip-Flops

JK Flip-Flops sind in zwei Haupttypen erhältlich: von Kanten ausgelöscht und ausgelöscht, jeweils für unterschiedliche Betriebsanforderungen ausgelegt.

Kanten-ausgelöste JK Flip-Flops: Ändern Sie ihren Zustand nur an bestimmten Stellen - wenn das Taktsignal von niedrig auf hoch (steigende Kante) oder hoch auf niedrig (fallende Kante) übergeht.Dieses Merkmal macht sie ideal für Systeme, bei denen genaues Timing bestehen.Da Zustandsänderungen genau am Rand der Uhr auftreten, stellen diese Flip-Flops sicher, dass alle Aktualisierungen synchron mit dem Taktpuls erfolgen.Dieses vorhersehbare Verhalten ist in eng gesteuerten Umgebungen wie digitalen Uhren, Registern und den meisten aufeinanderfolgenden Schaltungen dynamisch.Hier ist der Zeitpunkt jeder Änderung schwerwiegend für die Aufrechterhaltung der Systemstabilität und die Synchronisierung der Operationen.

Ebenen ausgelöste JK Flip-Flops: Aktivieren Sie unterschiedlich und reagieren Sie auf das Eingangssignal, solange das Taktsignal auf einem bestimmten Niveau liegt - ob hoch oder niedrig.Sie warten nicht auf einen bestimmten Uhrenübergang.Stattdessen ändert sich der Flip-Flop die Zustände.Dieses Verhalten macht die ausgestrahlten Flip-Flops besser für asynchrone Systeme geeignet, wobei Eingänge möglicherweise nicht mit einem regulären Taktpuls übereinstimmen.Sie bieten Flexibilität in Systemen, in denen Eingänge unvorhersehbar sind oder unregelmäßige Intervalle erreichen, z.

Vor- und Nachteile von JK Flip-Flop

JK Flip-Flops bieten mehrere Vorteile, verfügen jedoch auch über einige Kompromisse, die beim Entwerfen digitaler Systeme sorgfältig abgewogen werden müssen.

|

Profis |

|

|

Vielseitigkeit |

JK Flip-Flops sind sehr flexibel und können

in verschiedenen digitalen Schaltungen wie Speicherspeicher, Zähler und verwendet werden

Steuerungssysteme.Sie können basierend auf anderen Eingaben umschalten, einstellen oder zurücksetzen

Bedingungen, die sie für eine Vielzahl von Anwendungen geeignet machen, die

Erfordernde eine genaue Kontrolle über Zustandsübergänge. |

|

Selbstkorrekturmechanismus |

Eine der herausragenden Merkmale von JK

Flip-Flops ist die integrierte Rückkopplungsschleife, die die korrigierte korrigische Behebung hilft

Zustände dynamisch.Diese Selbstkorrektur stellt sicher, dass die Schaltung bleibt

Stabil während des Betriebs, auch wenn sich die Eingaben schnell ändern. |

|

Minderung der Rennbedingung |

Im Gegensatz zu einfacheren Flip-Flops, JK Flip-Flops

sind so konzipiert, dass Rassenbedingungen vorliegen - Einrichtungen, bei denen die Ausgabe wird

aufgrund widersprüchlicher Eingangssignale instabil.Diese Fähigkeit zu pflegen

Die konsistente Ausgabe verbessert auch unter schnellen und sequentiellen Eingangsänderungen die

Zuverlässigkeit der Schaltung. |

|

Nachteile |

|

|

Komplexes Design |

JK Flip-Flops sind komplizierter als

Grundlegende Flip-Flops.Ihr Design erfordert zusätzliche Logik -Tore und Eingaben

Überwachung, die den Schaltkreis erschweren kann, und es schwieriger zu entwerfen und

Fehlerbehebung, insbesondere in Systemen, in denen Einfachheit bevorzugt wird. |

|

Ausbreitungsverzögerung |

Das interne Gating zur Verwaltung des Status verwendet

Übergänge führen zu einer Verzögerung, wie schnell Signale verarbeitet werden können.In

Hochgeschwindigkeitsanwendungen kann diese Verzögerung das Gesamtzeitpunkt beeinflussen und langsamer werden

Die Leistung der Schaltung. |

|

Höherer Stromverbrauch |

Aufgrund ihrer Komplexität und der Notwendigkeit zu

Überwachen Sie die Eingabebedingungen ständig, JK Flip-Flops verbrauchen mehr Leistung

Im Vergleich zu einfacheren Flip-Flops.In größeren Systemen oder Energieempfindlichkeit

Anwendungen, dieser höhere Strombedarf kann zu einem Nachteil werden |

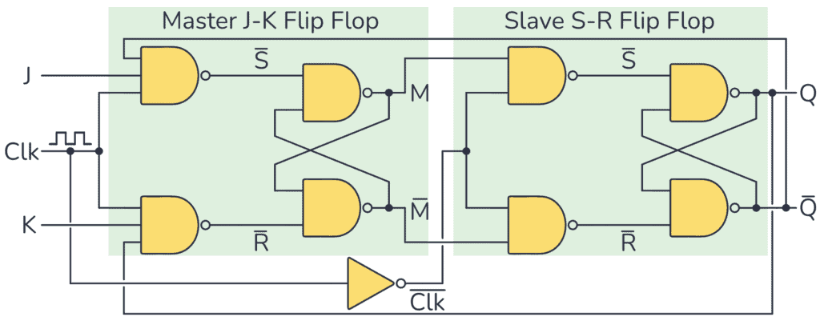

Abbildung 10: Master-Slave JK Flip-Flop

Dekodieren des Master-Slave JK Flip-Flop

Der Master-Slave-JK-Flip-Flop wurde entwickelt, um den in Standard-JK-Flip-Flops zu findenen Rennerkrankungen mit einem zweistufigen Prozess zur effizienten Verwaltung von Eingängen und Ausgängen zu lösen.

Die erste Stufe, die als Master -Stufe bezeichnet wird, erfasst die Eingangswerte, wenn das Taktsignal eine bestimmte Kante erreicht, die entweder steigt oder fällt.Zu diesem Zeitpunkt werden die Eingabedaten eingesperrt, was bedeutet, dass sich die weiteren Änderungen der Eingänge erst im nächsten Taktzyklus auf den erfassten Zustand auswirken.Diese Phase stellt sicher, dass der Flip-Flop die korrekte Eingabe registriert, ohne durch nachfolgende Änderungen während desselben Taktzyklus beeinflusst zu werden.

Nach Abschluss der Masterbühne kommt die Sklavenbühne ins Spiel.Diese Stufe aktualisiert die Ausgabe basierend auf den Daten, die von der Master -Stufe erfasst wurden, jedoch nur am nächsten Uhrenkandel.Durch die Trennung der Eingangserfassung von der Ausgangsaktualisierung stellt die Slave -Stufe sicher, dass die Ausgabe stabil bleibt, bis die Master -Stufe die Eingabe vollständig verarbeitet hat.Dies verhindert vorzeitige oder unbeabsichtigte Änderungen der Ausgabe während des Taktzyklus.

Warum ist die Master-Slave-Konfiguration wichtig?

Der zweistufige Prozess stabilisiert den Betrieb des JK-Flip-Flops und verhindert unerwünschte Oszillationen oder Schwankungen, die in einfacheren Konfigurationen auftreten können, insbesondere wenn beide Eingaben hoch gehalten werden.Durch die Entkopplung der Eingangsverarbeitung aus der Ausgangsänderung stellt die Master-Slave-Konfiguration sicher, dass die Ausgänge vorhersehbar und stabil bleiben, selbst in Situationen, in denen das Timing wertvoll ist.

Adressieren das Rennen um den Zustand in JK Flip-Flops

Rassenbedingungen treten in JK Flip-Flops auf, wenn beide Eingänge J und K hoch sind und das Taktsignal zu lange aktiv bleibt.Dies führt zu kontinuierlichem Umschalten der Ausgänge, die zu einem zu einem geratenen Verhalten führen und die Zuverlässigkeit der Schaltung stören können.

Das Master-Slave-Setup verwendet einen zweistufigen Prozess, um Rassenprobleme zu verhindern.Die Master -Stufe erfasst die Eingangswerte am Taktrand und sperrt sie ein. Die Slave -Bühne aktualisiert die Ausgänge am nächsten Taktrand und stellt sicher, dass sich die Ausgabe erst ändert, wenn die Eingänge vollständig verarbeitet sind.Dieser Ansatz verhindert effektiv, dass der Ausgang unkontrolliert umschaltet, auch wenn die Eingänge über einen längeren Zeitraum hoch bleiben.

Eine andere Methode, um Rassenbedingungen zu vermeiden, ist die Einstellung der Taktpulsdauer.Indem Sie den Taktpuls kürzer machen als die Ausbreitungsverzögerung des Flip-Flop-Ausbreitung, können Sie sicherstellen, dass sich der Zustand nicht mehr als einmal innerhalb des gleichen Taktzyklus ändert.Dies verhindert, dass der Flip-Flop während eines einzelnen Zyklus wiederholt umschaltet und die Ausgabe stabilisiert.

Dynamik des Schaltens in JK Flip-Flops

Das Schaltverhalten eines JK-Flip-Flop wird größtenteils durch das Timing des Taktsignals und die Eingangspegel (J und K) angetrieben.Der Flip-Flop ändert den Zustand basierend auf den an der positiven Rand des Taktsignals vorhandenen Eingänge.In diesem gefährlichen Moment bewertet der Flip-Flop die Eingaben und aktualisiert ihre Ausgabe entsprechend.

Wenn das Taktsignal die steigende Kante trifft, liest der JK Flip-Flop die aktuellen Zustände der J- und K-Eingänge.Abhängig von ihren Werten hält der Flip-Flop die Ausgabe entweder, setzen, zurücksetzen oder umschalten.

Digitale Uhren: Die Genauigkeit ist alles in digitalen Uhren, und JK Flip-Flops hilft bei der Aufrechterhaltung dieser Genauigkeit, indem sichergestellt wird, dass nur in Intervallen von Takten staatliche Änderungen auftreten.

Sequentielle Logik -Tester: In Systemen, die die Funktionalität von Logikschaltungen testen, spielen JK Flip-Flops eine Rolle bei der Überprüfung, ob jede Komponente korrekt auf bestimmte zeitgesteuerte Signale reagiert.

Andere zeitkritische Systeme: In verschiedenen digitalen Anwendungen, bei denen das Timing riskant ist, wie z. B. Kommunikationssysteme oder Datenverarbeitungseinheiten, stellt der JK-Flip-Flop sicher, dass Statusübergänge synchron mit der Uhr auftreten, wodurch Timing-Fehler verhindert werden.

Abschluss

Der JK Flip-Flop stammt als ultimatives Element in der digitalen Schaltungsdesign und bietet eine Mischung aus Vielseitigkeit und Präzision, die verzweifelt nach einer Vielzahl von Anwendungen von Speicherspeicher bis hin zu Frequenzabteilung und Synchronisation digitaler Prozesse reichen.Seine Fähigkeit, Rassenbedingungen durch innovative Konfigurationen wie die Master-Slave-Arrangement zu mildern, unterstreicht die Anpassungsfähigkeit bei der Lösung inhärenter Designherausforderungen.Ebenso unterstreicht die schwerwiegende Rolle des Flip-Flop bei der Gewährleistung der präzisen Zustandsübergänge ihre erforderliche Natur bei der Erstellung und Aufrechterhaltung zuverlässiger und effizienter digitaler Systeme.Mit dem Fortschritt der Technologie sind die sich entwickelnden Designs und Anwendungen des JK Flip-Flop weiterhin entscheidend, um die Grenzen der digitalen Elektronik in anspruchsvollere und robustere Architekturen zu überschreiten.

Häufig gestellte Fragen [FAQ]

1. Was sind die Anwendungen von JK Flip Flop?

Der JK Flip-Flop wird in digitaler Elektronik für eine Vielzahl von Aufgaben ausgiebig verwendet:

Timing -Anwendungen: Es kann als Verzögerungselement oder Timer dienen, wenn es in bestimmten Konfigurationen verbunden ist.

Zähler und Register: Durch den Umschalten des Zustands mit jedem Taktpuls wird es zum Entwerfen verschiedener Zähler und Verschiebungsregister verwendet, die in sequentiellen Logikschaltungen ultimativ sind.

Speicherspeicher: Es bietet eine grundlegende Speichereinheit, die beim Speichern von Bits in Rechenanwendungen nützlich ist.

2. Wie funktioniert ein JK Flip-Flop mit einer Wahrheitstabelle?

Ein JK Flip-Flop verfügt über zwei Eingänge (J und K) und ein Taktsignal.Der Betrieb variiert basierend auf den Eingangszuständen, die mit der Uhr synchronisiert sind:

• j = 0, k = 0: Die Ausgabe ändert sich nicht.

• J = 0, K = 1: Der Ausgang wird auf 0 zurückgesetzt.

• j = 1, k = 0: Die Ausgabe ist auf 1 gesetzt.

• j = 1, k = 1: Die Ausgabe umschaltet sich (d. H. Wenn es 0 war, wird es 1 und umgekehrt).

3. Was ist JK Flip Flop und funktioniert es?

Ein JK Flip-Flop kombiniert die Eigenschaften von SR- und T-Flip-Flops.Es vermeidet den in SR Flip-Flops beobachteten "verbotenen" Zustand, indem die JK-Eingänge effektiv verwendet werden:

Der Status des Flip-Flop wird durch die Eingänge J und K gesteuert, die feststellen, ob der Ausgang synchron mit der steigenden oder fallenden Kante des Taktpulses synchronisiert, zurückgesetzt, eingestellt oder umschalten sollte.

4. Was sind die Anwendungen von Riegel und Flip-Flops?

Datenspeicherung: Riegel und Flip-Flops sind für die Datenspeicherung innerhalb von Registern und Speicherarrays schwerwiegend.

Frequenzabteilung: Wird in Frequenzteilern aufgrund ihrer Fähigkeit verwendet, Zustände an Taktkanten zu ändern, und halbiert die Frequenz mit jeder Stufe in einer Serie.

Staatsmaschinen: Grundlegend bei der Gestaltung von Finite -Status -Maschinen, die zur Implementierung sequentieller Logik- und Steuerungsschaltungen verwendet werden.

Debouncing: Wird verwendet, um Signale von mechanischen Schalter und Tasten zu stabilisieren, um einzelne, saubere Übergänge zu gewährleisten.

5. Wofür werden Flip-Flops verwendet?

Binärspeicher: Jedes Flip-Flop speichert ein Stück Daten, sodass sie Bausteine für Binärspeichergeräte erstellen.

Uhrendrenner: Sie teilen die Eingangsaktuhrenfrequenz um zwei, nützlich in digitalen Uhren und Timing -Anwendungen.